- Inicio

- Quem somos

- Produtos

-

Marcas

-

Produtos por Medida

- Analisadores Vibração

- Bombas Peristálticas

- Fluxo de Ar

- CO Monóxido Carbono

- Contadores Geiger

- Destiladores

- Espectrofotometria

- Esterilização

- Fluorescência

- GEOTECNICS

- Umidade do Solo

- Índice de área foliar

- Chuva (pluviométrico)

- Meteorologia

- Nível de Água

- O2 oxigênio

- pH

- Pressão Diferencial

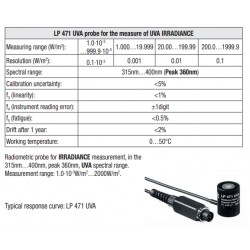

- Radiação

- Salinidade/Condutivid.

- Telemetria

- Velocidade do Ar

- Umidade Relativa

- Veterinary

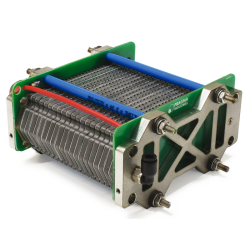

- PILHAS DE COMBUSTÍVEL

- Analisadores de Redes

- Calibradores

- CAUDAL DE ÁGUA

- Cor / Colorímetro

- Contadores Partículas

- Direçao Vento

- Espectrometria

- Evapotranspiração

- Fotossíntese

- Rachaduras edifícios

- Inspeção de Tubos

- Luz Quântica

- Movimento e GPS

- Nível de diesel

- Oxigênio Dissolvido DO

- Pressão Atmosférica

- Radon

- Savia/Fluxo de Savia

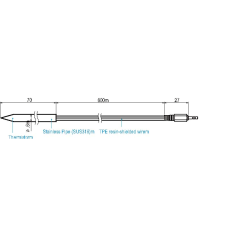

- Temperatura

Scientech110 Plataforma de Desenvolvimento Universal para FPGAs, CPLDs, CPLDs Cool Runner de Xilinx, etc.

Scientech TechBooks são plataformas de aprendizado compactas e fáceis de usar para fornecer uma maneira moderna, portátil, abrangente e prática de aprender tecnologia. Cada TechBook é fornecido com material de aprendizagem multimídia detalhado que cobre manual inteligente com tutorial de linguagem, exemplos, laboratórios, códigos de exemplo em Verilog / VHDL, teoria básica, procedimento passo a passo para conduzir a experiência e outras informações úteis.

Scientech110 Plataforma de Desenvolvimento Universal para FPGAs, CPLDs, CPLDs Cool Runner de Xilinx, etc.

Eu aceito política de privacidade regras

A Plataforma de Desenvolvimento Universal Scientech 110 foi projetada para fornecer uma maneira rápida e fácil de aprender a frente e design embutido VLSI. Baseia-se no conceito de cartão mãe-mãe para projetos VLSI que visam os FPGAs, CPLDs, CPLDs Cool Runner da Xilinx e também pode ser usado em lobs embutidos usando a placa filha ARM7. A plataforma de desenvolvimento contém entrada-saída, ADC, DAC, Displays, teclado e periféricos, que podem ser usados para aprender e implementar projetos VLSI básicos e avançados.

Scientech 110, Universal Development Platform é uma plataforma ideal para melhorar educação, treinamento, habilidades e desenvolvimento entre as mentes jovens.

Especificações da placa mãe:

- A bordo: + 5V, 3.3V, 2.5V, fornecimento de 1.8V

Visor LCD: 16 X 2 Character LCD

Segmento 7: 4 dígitos

8 canais ADC: resolução de 8 bits

Botão: 4

LEDs de saída: 16

Interruptores DIP: 16

Teclado HEX: 1

DAC: resolução de 8 bits

Memória: SRAM 32KB

Interface periférica: Serial, PS2, VGA, USB etc. E / S grátis para

Cartão filha do braço 7

FPGA Daughter Card

- Família Xilinx: Spartan 3, XC3S400PQ208

- Densidade do dispositivo: portões de 400k

- A bordo: 8 MHZ de cristal

- Chave de redefinição mestre: para reinicialização de hardware

- A bordo: EPROM para inicialização FPGA.

- Método de configuração: JTAG / interface de verificação de limites

: Interface PROM

CPLD Daughter Card

- Família Xilinx: CPLD, XC95108TQ100

- Densidade do dispositivo: 2400 portões, 108 células macro

- A bordo: 8 MHZ de cristal

- Método de configuração: interface JTAG (verificação de limite)

Cool Runner CPLD Daughter Card: (Opcional)

Família Xilinx:

- Cool Runner: XCR3128

- Pacote: VQ100

Densidade do dispositivo:

- 28 macrocélulas

Métodos de configuração:

- IEEE 1149 JTAG Interface (Boundary Scan)

Spartan3E FPGA Daughter Card: (Opcional)

- Família Xilinx: Spartan 3E, XC3S500EPQ208

- Densidade do dispositivo: portões de 500k

- A bordo: 8 MHZ de cristal

- Chave de redefinição mestre: para reinicialização de hardware

- A bordo: EPROM para inicialização FPGA.

- Método de configuração: interface de varredura JTAG / Boundary,

: Interface PROM

Spartan3A FPGA Daughter Card: (Opcional)

- Família Xilinx: Spartan 3A, XC3S50-ATQFP144

- Densidade do dispositivo: 50k portas / 1584 células lógicas

- A bordo: EPROM para inicialização FPGA.

- Método de configuração: interface de varredura JTAG / Boundary,

: Interface PROM

-Spartan6 FPGA Daughter Card: (Opcional)

- Família Xilinx: Spartan 6, XC6SLX9 TQ144

- Densidade do dispositivo: células lógicas 9152

- A bordo: EPROM para inicialização FPGA.

- Método de configuração: interface de varredura JTAG / Boundary,

: Interface PROM

ARM7 Daughter Card: (Opcional)

Família do Dispositivo:

- Philips Semiconductor: LPC2292 / 94

- Pacote: LQFP144

Densidade do dispositivo:

- Microcontrolador ARM de 16/32 bits

- Memória flash de 256 KB

Métodos de configuração:

- Interface JTAG

- Interface RS232

Altera Cyclone II FPGA Daughter Card (opcional)

- Dispositivo - EP2C8Q208C8

- Família - Ciclone II

- Número de elementos / células -8250

- Número de entrada dedicada gratuita -5

- Número de relógios-2

- Configuração USB Blaster Cable quartus -II web adition

- Cartão periférico:

- RS232 (porta serial)

- Porta VGA

- porta PS2

- Porta USB (Serial para USB)

Logótipos Booleanos Digitais, Multiplexadores, De-multiplexadores

Codificadores, Decodificador, codificador de prioridade, conversor de código, paridade

Gerador, travas e flip-flop, registros de deslocamento, contador BCD,

Decodificadores de endereço, ALU, MAC, Interface de tela LCD 16X2,

Interface do teclado HEX, design IP Core do Porto Serial, PS2,

VGA, ADC, DAC, SRAM etc.

Acessórios Incluídos

- Cabo JTAG FPGA / CPLD: 1 No.

- Cabo Xilinx USB JTAG (opcional): 1No.

- Cabo serial fêmea para homem: 1 No.

- Cabo USB: 1 No.

- Fonte de alimentação +12 V: 1 No.

- Xilinx ise Webpack

- Categoria

- FPGA